1. Tujuan

1. Mengetahui karakteristik dan prinsip kerja rangkaian Fixed-Bias Configuration

2. Membuat simulasi rangkaian di software

2. Komponen

1. Baterai

Baterai sebagai sumber tegangan pada rangkaian

2. Resistor

Resistor sebagai penghambat arus pada rangkaian

3. Ground

Ground sebagai system pentanahan pada rangkaian

4. DC Generator

Sebagai penghasil sumber energy listrik pada rangkaian

5. JFET

Sebagai penguat pada rangkaian

3. Dasar Teori

Pengaturan biasing paling sederhana untuk n-channel JFET muncul pada Gambar 6.1. Disebut sebagai konfigurasi tetap-bias, itu adalah salah satu dari beberapa konfigurasi FET yang dapat diselesaikan seperti secara langsung menggunakan pendekatan matematika atau grafis. Kedua metode dimasukkan dalam bagian ini untuk menunjukkan perbedaan antara kedua filosofi dan juga untuk menetapkan fakta bahwa solusi yang sama dapat diperoleh dengan menggunakan kedua metode tersebut.

Konfigurasi Gambar 6.1 meliputi level ac Vi dan Vo dan kapasitor kopling (C1 dan C2). Ingat bahwa kapasitor kopling adalah "sirkuit terbuka" untuk analisis dc dan impedansi rendah (pada dasarnya sirkuit pendek) untuk analisis ac. Resistor RG hadir untuk memastikan bahwa Vi muncul pada input ke amplifier FET untuk analisis ac (Bab 9). Untuk analisis dc,

Penurunan tegangan nol pada RG memungkinkan untuk mengganti RG dengan ekivalensi hubung singkat, seperti yang muncul dalam jaringan Gambar 6.2 yang secara khusus digambar ulang untuk analisis dc.

Fakta bahwa terminal negatif baterai terhubung langsung ke potensi positif VGS yang jelas menunjukkan bahwa polaritas VGS berbanding terbalik dengan VGG. Menerapkan hukum tegangan Kirchhoff ke arah searah jarum jam dari Gambar 6.2 yang ditunjukkan akan menghasilkan

Karena VGG adalah pasokan dc tetap, tegangan VGS tetap besarnya, sehingga menghasilkan notasi "konfigurasi bias tetap." Level yang dihasilkan dari drain current ID sekarang dikendalikan oleh persamaan Shockley:

Karena VGS adalah kuantitas tetap untuk konfigurasi ini, besarnya dan tandanya dapat dengan mudah disubstitusikan ke dalam persamaan Shockley dan tingkat ID yang dihasilkan dihitung. Ini adalah salah satu dari beberapa contoh di mana solusi matematika untuk konfigurasi FET cukup langsung.

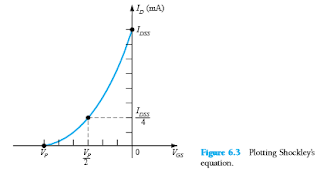

Analisis grafis akan membutuhkan plot persamaan Shockley seperti yang ditunjukkan pada Gambar 6.3. Ingatlah bahwa memilih VGS VP / 2 akan menghasilkan arus yang menguras IDSS / 4 saat merencanakan persamaan. Untuk analisis bab ini, tiga titik yang ditentukan oleh IDSS, VP, dan persimpangan yang baru saja dijelaskan akan cukup untuk memplot kurva.

Pada Gambar 6.4, level tetap VGS telah ditumpangkan sebagai garis vertikal pada VGS VGG. Pada titik mana pun pada garis vertikal, level VGS adalah VGG — level ID harus ditentukan pada garis vertikal ini. Titik di mana dua kurva

intersect adalah solusi umum untuk konfigurasi — umumnya disebut sebagai titik diam atau operasi. Subskrip Q akan diterapkan untuk mengalirkan tegangan arus dan gerbang-ke-sumber untuk mengidentifikasi levelnya pada titik-Q. Perhatikan pada Gambar 6.4 bahwa level diam ID ditentukan dengan menggambar garis horizontal dari titik-Q ke sumbu ID vertikal seperti yang ditunjukkan pada Gambar 6.4. Penting untuk disadari bahwa begitu jaringan Gambar 6.1 dibangun dan beroperasi, level dc ID dan VGS yang akan diukur oleh meter Gambar 6.5 adalah nilai diam yang ditentukan oleh Gambar 6.4.

Tegangan drain-ke-sumber dari bagian output dapat ditentukan dengan menerapkan hukum tegangan Kirchhoff sebagai berikut:

Ingat bahwa tegangan subskrip tunggal merujuk pada tegangan pada suatu titik sehubungan dengan arde. Untuk konfigurasi Gambar 6.2,

Menggunakan notasi dua subskrip:

tambahan

Fakta bahwa VD VDS dan VG VGS cukup jelas dari kenyataan bahwa VS 0 V, tetapi derivasi di atas dimasukkan untuk menekankan hubungan yang ada antara notasi rangkap-rangkap dan rangkap-rangkap. Karena konfigurasi membutuhkan dua suplai dc, penggunaannya terbatas dan tidak akan dimasukkan dalam daftar konfigurasi FET yang paling umum.

Contoh Soal :

(a) VGSQ.

(b) IDQ.

(c) VDS.

(d) VD.

(e) VG.

(f) VS.

Penyelesaian :

(a) VGSQ VGG 2 V

(b) IDQ IDSS 1 V V G P S 2 10 mA 1 2 8

V V 2 10 mA(1 0.25)2 10 mA(0.75)2 10 mA(0.5625) 5.625 mA

V V 2 10 mA(1 0.25)2 10 mA(0.75)2 10 mA(0.5625) 5.625 mA

(c) VDS VDD IDRD 16 V (5.625 mA)(2 k ) 16 V 11.25 V 4.75 V

(d) VD VDS 4.75 V

(e) VG VGS 2 V

(f) VS 0 V

4.Prinsip Kerja

Rangkaian bias tetap (fix bias) untuk transistor ini cukup sederhana karena hanya terdiri atas dua resistor RB dan RC. Kapasitor C1 dan C2 merupakan kapasitor kopling yang berfungsi mengisolasi tegangan dc dari transistor ke tingkat sebelum dan sesudahnya, namun tetap menyalurkan sinyal ac-nya. Rangkaian dasar untuk memberikan fix bias pada transistor dapat dilihat pada gambar berikut.

Rangkaian Dasar Fix Bias Pada Transistor

Fungsi kapasitos C1 dan C2 adalah kopling input dan output seperti dijelaskan diatas, sehingga untuk analisa DC rangkaian fix bias transistor menjadi seperti berikut.

Rangkaian Analisa DC Fix Bias Transistor

Dari gambar rangkaian DC diatas dapat dirumuskan nilai arus basis IB sebagai berikut :

Dari nilai IB tersebut maka dapat diketahui nilai IC

Karena VCC dan VBE tetap, maka RB adalah penentu arus basis pada titik kerja transistor dengan tegangan bias tetap seperti rangkaian diatas.

5. Gambar

6. Video

7. Link Download <Kembali>

Gambar <Disini>

Video <Disini>

Tidak ada komentar:

Posting Komentar