PERCOBAAN 2

[KEMBALI KE MENU SEBELUMNYA]

1. Jurnal [Kembali]

1. AND Gate

Gerbang AND memerlukan 2 atau lebih Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang AND akan menghasilkan Keluaran (Output) Logika 1 jika semua masukan (Input) bernilai Logika 1 dan akan menghasilkan Keluaran (Output) Logika 0 jika salah satu dari masukan (Input) bernilai Logika 0. Simbol yang menandakan Operasi Gerbang Logika AND adalah tanda titik (“.”) atau tidak memakai tanda sama sekali. Contohnya : Z = X.Y atau Z = XY.

2. OR Gate

Gerbang OR memerlukan 2 atau lebih Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang OR akan menghasilkan Keluaran (Output) 1 jika salah satu dari Masukan (Input) bernilai Logika 1 dan jika ingin menghasilkan Keluaran (Output) Logika 0, maka semua Masukan (Input) harus bernilai Logika 0. Simbol yang menandakan Operasi Logika OR adalah tanda Plus (“+”). Contohnya : Z = X + Y.

3. XOR Gate

X-OR adalah singkatan dari Exclusive OR yang terdiri dari 2 Masukan (Input) dan 1 Keluaran (Output) Logika. Gerbang X-OR akan menghasilkan Keluaran (Output) Logika 1 jika semua Masukan-masukannya (Input) mempunyai nilai Logika yang berbeda. Jika nilai Logika Inputnya sama, maka akan memberikan hasil Keluaran Logika 0.

4. LogicProbe

sebagai keluaran atau output dari gerbang logika

5. Logic State

Sebagai masukan atau input dari gerbang logika

Pada rangkaian yang diatas, pada gerbang XOR input yang diberikan berlogika 1 (pada titik B) dan 0 (pada titik D) sehingga menghasilkan output 1. Pada gerbang AND, inputnya berlogika 0 (pada titik A, C', dan D) sehingga menghasilkan output berlogika 0. Output dari kedua gerbang tersebut diteruskan ke gerbang OR dan menjadi input bagi gerbang OR tersebut sehingga menghasilkan output baru dengan logika 1.

Pada rangkaian yang dibawah, pada gerbang XOR input yang diberikan sama yaitu 1 (pada titik B) dan 0 (pada titik D) sehingga menghasilkan output berlogika 1. Pada gerbang AND, terdapat 2 input berlogika 0 (titik A dan B') dan input berlogika 1 (pada titik C) sehingga menghasilkan output berlogika 0. Output dari kedua gerbang tersebut diteruskan ke gerbang OR dan menjadi input bagi gerbang OR tersebut sehingga menghasilkan output baru dengan logika 1.

1). Sederhanakan persamaan aljabar boolean pada percobaan 2 sehingga didapat dua persamaan H1 dan H2

Jawab :

Dengan persamaan akhir nya B'D + BD' + ABC'D, maka persamaan tersebut dapat dipecah menjadi

Sehingga rumus persamaan untuk H1 dan H2 adalah

2). Jelaskan minimal 5 buah hukum aljabar bolean

Jawab :

-. Hukum Komutatif

Hukum Komutatif menjelaskan bahwa penukaran atau perubahan urutan variabel input atau sinyal masukan sama sekali tidak mempengaruhi variabel output suatu rangkaian logika.

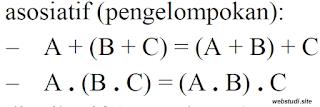

-. Hukum Asosiatif

Hukum Asosiatif menjelaskan bahwa perubahan urutan penyelesaian operasi pada variabel tidak akan mempengaruhi variabel output suatu rangakaian logika.

-. Hukum Ditributif

Hukum Distributif menyatakan bahwa variabel-variabel atau sinyal Input dapat disebarkan tempatnya atau diubah urutan sinyalnya, perubahan tersebut tidak akan mempengaruhi Output Keluarannya. -. Hukum Inversi

Hukum Inversi menggunakan Operasi Logika NOT. Hukum Inversi ini menyatakan jika terjadi Inversi ganda (kebalikan 2 kali) maka hasilnya akan kembali ke nilai aslinya.

Jadi, jika suatu Input (masukan) diinversi (dibalik) maka hasilnya akan berlawanan. Namun jika diinversi sekali lagi, hasilnya akan kembali ke semula.

-. Hukum Absorsbsi, Kombinasi dan Konsensus

7. Link Download [Kembali]

Tidak ada komentar:

Posting Komentar